[MIPS] RFE instruction not present.

See original GitHub issueThe MIPS instruction set contains an instruction called “RFE”, for “Return From Exception”. Its encoding is well specified, with no parameters: http://people.cs.pitt.edu/~don/coe1502/current/Unit4a/Unit4a.html

This document translates “RFE” to the opcode 0x42000010

The point of the RFE instruction is to restore cop0 status flags atomically while returning to the user space. Its pseudo-code implementation can be seen as the following:

COP0.Status = (COP0.Status & 0xfffffff0) | ((COP0.Status & 0x3c) >> 2);

The explanation of this behavior is simple: when triggering an exception, the MIPS CPU does the following atomically, in order to save usermode flags:

COP0.Status = (COP0.Status & ~0x3f) | (CP0.Status & 0xf) << 2);

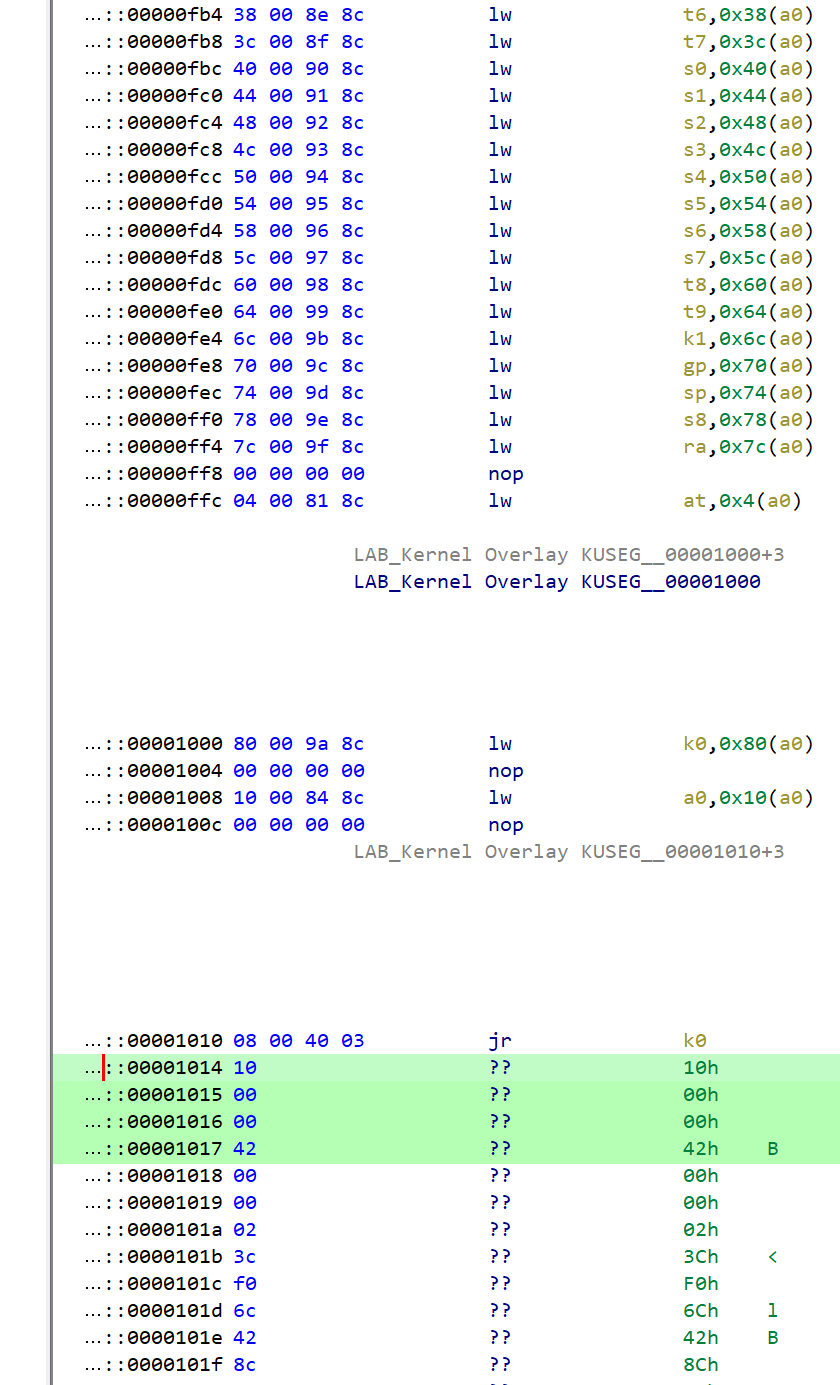

When disassembling a MIPS exception handler from a MIPS kernel with ghidra, it will currently fail to disassemble that instruction properly, nor recognize it as even an executable instruction:

Issue Analytics

- State:

- Created 3 years ago

- Comments:8 (4 by maintainers)

Top Related StackOverflow Question

Top Related StackOverflow Question

Has been fixed and should be in patch and master soon. Thanks for fixing.

Oh, that’s correct. I cleared the whole function and re-disassembled it, and now the underscore shows up.

Thanks!